# ezv technologies

# CCD42-90 Back Illuminated High Performance CCD Sensor

#### FEATURES

- 2048 by 4608 Pixel Format

- 13.5 μm Square Pixels

- Image Area 27.6 x 62.2 mm

- Back Illuminated Format for High Quantum Efficiency

- Low Noise Output Amplifiers

- Wide Dynamic Range

- Symmetrical Anti-static Gate Protection

- 3-side Buttable Package

- Gated Dump Drain on Readout Register

- Flatness better than 15 μm peak to valley

# APPLICATIONS

- Astronomy

- Scientific Imaging

# INTRODUCTION

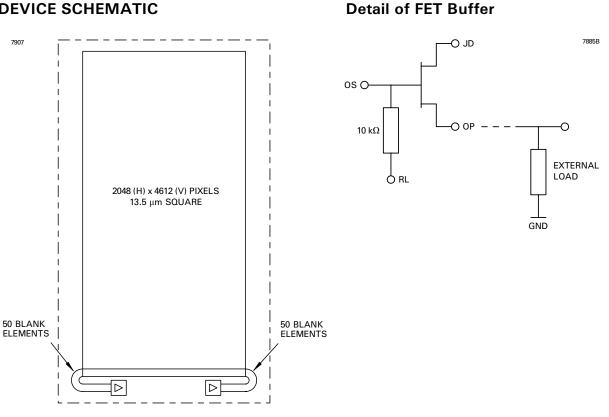

This version of the CCD42 family of CCD sensors has full-frame architecture. Back illumination technology, in combination with an extremely low noise amplifier, makes the device well suited to the most demanding applications, such as astronomy.

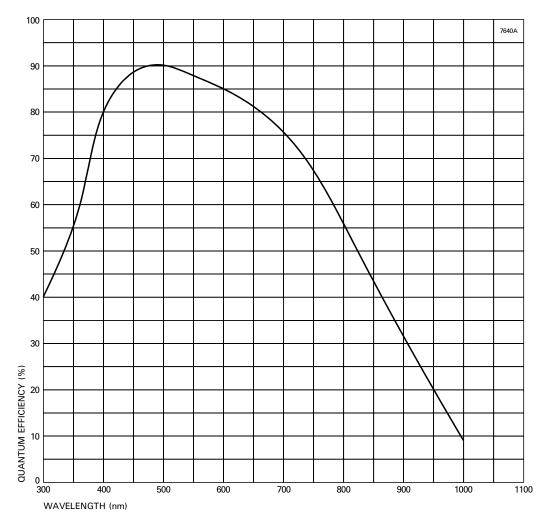

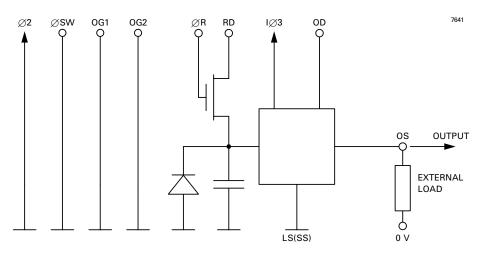

The output amplifier is designed to give excellent noise levels at low pixel rates and can match the noise performance of most conventional scientific CCDs at pixel rates as high as 1 MHz. The low output impedance and optional FET buffer simplify the interface with external electronics.

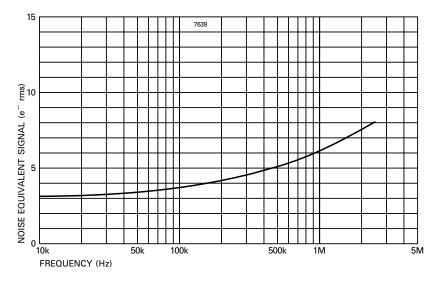

The readout register has a gate controlled dump-drain to allow fast dumping of unwanted data. The register is designed to accommodate four image pixels of charge and a summing well is provided capable of holding six image pixels. The output amplifier has a feature to enable the responsivity to be reduced, allowing the reading of such large charge packets.

The device is supplied in a package designed to facilitate the construction of large close-butted mosaics and is designed to be used cryogenically. The design of the package will ensure that the device flatness is maintained at the working temperature.

The sensor is shipped in a protective container, but no permanent window is fitted.

# **TYPICAL PERFORMANCE (at 173 K)**

| Pixel readout frequency .    |  |  | 20 -  | 3000  | kHz                    |

|------------------------------|--|--|-------|-------|------------------------|

| Output amplifier sensitivity |  |  |       | . 4.5 | µV/e <sup>−</sup>      |

| Peak signal                  |  |  |       | 150   | ke <sup>-</sup> /pixel |

| Spectral range               |  |  | 200 - | 1060  | nm                     |

| Readout noise (at 20 kHz)    |  |  |       | . 3   | e <sup>-</sup> rms     |

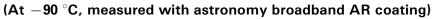

| QE at 500 nm                 |  |  |       | 90    | %                      |

| Charge transfer efficiency   |  |  |       | 99.9  | 995 %                  |

# **GENERAL DATA**

#### Format

| Image area    |         |     |      |        |     |     |    | 27.6 x 62.2 | mm |

|---------------|---------|-----|------|--------|-----|-----|----|-------------|----|

| Active pixels | (H)     |     |      |        |     |     |    | . 2048      |    |

|               | (∨)     |     |      |        |     |     |    | 4608 + 4    |    |

| Pixel size .  |         |     |      |        |     |     |    | 13.5 x 13.5 | μm |

| Number of o   | utput   | am  | plif | iers   |     |     |    | 2           |    |

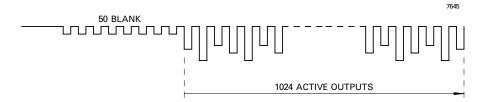

| Number of u   | ndersc  | an  | (se  | erial  | ) p | ixe | ls | 50          |    |

| The device h  | as a 10 | 20% | 6 f  | ill fa | act | or. |    |             |    |

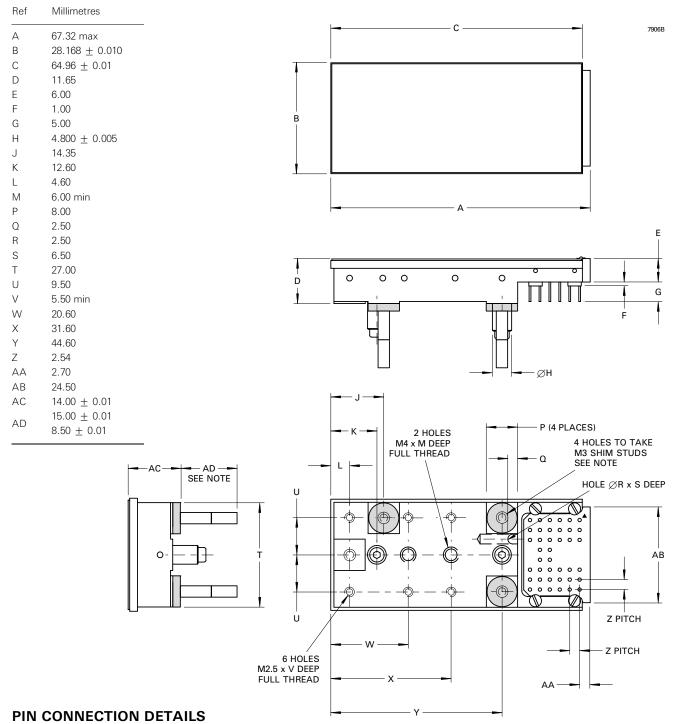

#### Package

| Format                 | invar r | neta | al pa | cka | ge with PGA o   | connector |

|------------------------|---------|------|-------|-----|-----------------|-----------|

| Focal plane height abo | ove ba  | se   |       |     | 14.0            | mm        |

| Package size           |         |      |       |     | 28.2 x 67.3     | mm        |

| Package weight         |         |      |       |     | 150             | g approx  |

| Number of pins         |         |      |       | •   | 40              |           |

| Inactive edge spacing: |         |      |       |     |                 |           |

| sides                  |         |      |       |     | 260 <u>+</u> 50 | μm        |

| top                    |         |      |       |     |                 | μm        |

| bottom (edge conne     | ection  | s)   |       |     | 5.0             | mm        |

e2v technologies (uk) limited, Waterhouse Lane, Chelmsford, Essex CM1 2QU, UK Telephone: +44 (0)1245 493493 Facsimile: +44 (0)1245 492492 e-mail: enquiries@e2v.com Internet: www.e2v.com Holding Company: e2v technologies plc

e2v technologies inc. 4 Westchester Plaza, PO Box 1482, Elmsford, NY10523-1482 USA Telephone: (914) 592-6050 Facsimile: (914) 592-5148 e-mail: enquiries@e2vtechnologies-na.com

© e2v technologies (uk) limited 2006

A1A-100026 Issue 8, March 2006 411/9572

#### PERFORMANCE (at 173 K unless stated)

|                                                                             | Min              | Typical            | Max  |                            |

|-----------------------------------------------------------------------------|------------------|--------------------|------|----------------------------|

| Peak charge storage (see note 1)                                            | 100k             | 150k               | -    | e <sup>-</sup> /pixel      |

| Peak output voltage (unbinned)                                              |                  | 675                |      | mV                         |

| Dark signal at 153 K (see note 2)                                           |                  | <0.1               | 1    | e <sup>-</sup> /pixel/hour |

| Charge transfer efficiency (see note 3):<br>parallel<br>serial              | 99.999<br>99.999 | 99.9995<br>99.9995 |      | %<br>%                     |

| Output amplifier sensitivity (see note 4)                                   | 3.0              | 4.5                | 6.0  | μV/e <sup>-</sup>          |

| Readout noise (see note 5)                                                  | -                | 3                  | 4    | rms e <sup>-</sup> /pixel  |

| Readout frequency (see note 6)                                              | -                | 20                 | 3000 | kHz                        |

| Output node capacity (see note 4):<br>OG2 low (mode 1)<br>OG2 high (mode 2) |                  | 200k<br>1000k      |      | electrons<br>electrons     |

| Serial register capacity                                                    | -                | 600k               | -    | e <sup>-</sup> /pixel      |

#### Spectral Response at 173 K (Astronomy broadband devices)

|                 | Spectral Resp | oonse (QE) | Response                          |   |

|-----------------|---------------|------------|-----------------------------------|---|

| Wavelength (nm) | Typical       | Min        | Non-uniformity, max (1 $\sigma$ ) |   |

| 350             | 50            | 40         | _                                 | % |

| 400             | 80            | 70         | 3                                 | % |

| 500             | 90            | 80         | -                                 | % |

| 650             | 80            | 75         | 3                                 | % |

| 900             | 30            | 25         | 5                                 | % |

Note Devices with alternate spectral response are also available.

# ELECTRICAL INTERFACE CHARACTERISTICS

#### Electrode capacitances (measured at mid-clock level)

|                                        | Min | Typical | Max |    |

|----------------------------------------|-----|---------|-----|----|

| $I \emptyset / I \emptyset$ interphase | -   | 35      | -   | nF |

| RØ/RØ interphase                       | -   | 80      | -   | pF |

| IØ/SS                                  | -   | 70      | -   | nF |

| RØ/SS                                  | -   | 150     | -   | pF |

| Output impedance                       | -   | 350     | -   | Ω  |

#### NOTES

- 1. Signal level at which resolution begins to degrade.

- 2. Dark signal is typically measured at 188 K and V\_{ss} = +9 V. The dark signal at other temperatures may be estimated from:

$$Q_d/Q_{d0} = 122T^3 e^{-6400/T}$$

where  $Q_{\rm d0}$  is the dark current at 293 K.

- 3. Measurements made using charge generated by X-ray photons of known energy. Charge transfer efficiency is measured for a complete three-phase triplet.

- 4. Operation of the OG2 gate modifies the output node. OG2

= LO (mode 1) is normally used for low noise, high responsivity. See also note 9.

- 5. Measured using a dual-slope integrator technique (i.e. correlated double sampling) with a 10  $\mu s$  integration period with OG2 = OG1 + 1 V.

- 6. Readout above 3000 kHz can be achieved but performance to the parameters given cannot be guaranteed.

## TYPICAL SPECTRAL RESPONSE

TYPICAL OUTPUT CIRCUIT NOISE (Measured using clamp and sample, temperature range 140 - 230 K)

### **BLEMISH SPECIFICATION**

| Traps           | Pixels where charge is temporarily held. Traps are counted if they have a capacity greater than $200 e^-$ at 173 K.                                                                                                                                                                    |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Slipped columns | Are counted if they have an amplitude greater than 200 $e^$                                                                                                                                                                                                                            |

| Black spots     | Are counted when they have a responsivity of less than 80% of the local mean signal.                                                                                                                                                                                                   |

| White spots     | Are counted when they have a generation rate equivalent to 100 electrons per pixel per hour at 153 K (typically measured at 188 K). The typical temperature dependence of white spot blemishes is the same as that of the average dark signal, i.e.: $Q_d/Q_{d0} = 122T^3 e^{-6400/T}$ |

| Column defects  | A column which contains at least 100 white                                                                                                                                                                                                                                             |

or black defects.

| GRADE                              | 0   | 1    | 2    | 3    |

|------------------------------------|-----|------|------|------|

| Column defects<br>(black or white) | 2   | 6    | 12   | 24   |

| White spots                        | 300 | 450  | 800  | 1200 |

| Traps                              | 15  | 30   | 50   | 75   |

| Total spots<br>(black and white)   | 900 | 1350 | 2000 | 3000 |

GRADE 5

Devices which are fully functional, with image quality below that of grade 3, and which may not meet all other performance parameters; not all parameters may be tested.

# **CLOCK ARCHITECTURE**

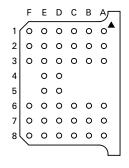

# CONNECTIONS, TYPICAL VOLTAGES AND ABSOLUTE MAXIMUM RATINGS 40-pin PGA connector

|                              |                 |                                             | CLOCK          |     | OCK HIGH               |     |                                 |

|------------------------------|-----------------|---------------------------------------------|----------------|-----|------------------------|-----|---------------------------------|

|                              |                 |                                             | LOW<br>Typical |     | DC LEVEL (V            |     | MAXIMUM RATINGS                 |

| PIN                          | REF             | DESCRIPTION                                 |                | Min | Typical                | Max | with respect to V <sub>SS</sub> |

| A1, A8,<br>C1, C8,<br>F2, F7 | V <sub>SS</sub> | Substrate                                   | n/a            | 0   | 9                      | 10  | -                               |

| D8                           | IØ1             | Image area clock, phase 1                   | 0              | 8   | 10                     | 15  | <u>+</u> 20 V                   |

| E8                           | IØ2             | Image area clock, phase 2                   | 0              | 8   | 10                     | 15  | ±20 V                           |

| F8                           | IØ3             | Image area clock, phase 3                   | 0              | 8   | 10                     | 15  | ±20 V                           |

| D4                           | RØ1(L)          | Register clock phase 1 (left)               | 1              | 9   | 11                     | 15  | <u>+</u> 20 V                   |

| E4                           | RØ2(L)          | Register clock phase 2 (left)               | 1              | 9   | 11                     | 15  | <u>+</u> 20 V                   |

| D5                           | RØ1(R)          | Register clock phase 1 (right) (see note 7) | 1              | 9   | 11                     | 15  | <u>+</u> 20 V                   |

| E5                           | RØ2(R)          | Register clock phase 2 (right) (see note 7) | 1              | 9   | 11                     | 15  | <u>+</u> 20 V                   |

| F6                           | RØ3             | Register clock phase 3                      | 1              | 9   | 11                     | 15  | <u>+</u> 20 V                   |

| E3                           | ØR(L)           | Reset gate (left)                           | 0              | 9   | 12                     | 15  | <u>+</u> 20 V                   |

| E6                           | ØR(R)           | Reset gate (right)                          | 0              | 9   | 12                     | 15  | <u>+</u> 20 V                   |

| E2                           | ØSW(L)          | Summing well gate (left)                    | 0              | 9   | 11                     | 15  | ±20 V                           |

| E7                           | ØSW(R)          | Summing well gate (right)                   | 0              | 9   | 11                     | 15  | ±20 V                           |

| F3                           | DG              | Dump gate (see note 8)                      | 0              | -   | 12                     | 15  | <u>+</u> 20 V                   |

| D3                           | OG1(L)          | Output gate 1 (left)                        | n/a            | 2   | 3                      | 4   | ±20 V                           |

| D6                           | OG1(R)          | Output gate 1 (right)                       | n/a            | 2   | 3                      | 4   | <u>+</u> 20 V                   |

| B2                           | DD(L)           | Dump drain (left)                           | n/a            | 20  | 24                     | 26  | -0.3 to +30 V                   |

| B7                           | DD(R)           | Dump drain (right)                          | n/a            | 20  | 24                     | 26  | -0.3 to +30 V                   |

| D2                           | OG2(L)          | Output gate 2 (left) (see note 9)           | 4              | 16  | 20                     | 24  | <u>+</u> 20 V                   |

| D7                           | OG2(R)          | Output gate 2 (right) (see note 9)          | 4              | 16  | 20                     | 24  | ±20 V                           |

| B1                           | OD(L)           | Output drain (left)                         | n/a            | 27  | 29                     | -   | -0.3 to +35 V                   |

| B8                           | OD(R)           | Output drain (right)                        | n/a            | 27  | 29                     | -   | -0.3 to +35 V                   |

| A2                           | OS(L)           | Output source (left)                        | n/a            |     | see note 10            |     | -0.3 to +25 V                   |

| A7                           | OS(R)           | Output source (right)                       | n/a            |     | see note 10            |     | -0.3 to +25 V                   |

| C2                           | RD(L)           | Reset drain (left)                          | n/a            | 15  | 17                     | -   | -0.3 to +25 V                   |

| C7                           | RD(R)           | Reset drain (right)                         | n/a            | 15  | 17                     | -   | -0.3 to +25 V                   |

| Optiona                      | l connectio     | ons for 309 JFET                            | 1              |     |                        |     |                                 |

| A3                           | RL(L)           | Load resistor (left)                        |                |     | A <sub>GND</sub> (0 V) |     |                                 |

| A6                           | RL(R)           | Load resistor (right)                       |                |     | A <sub>GND</sub> (0 V) |     |                                 |

| B3                           | OP(L)           | JFET source (left)                          |                |     | see note 11            |     |                                 |

| B6                           | OP(R)           | JFET source (right)                         |                |     | see note 11            |     |                                 |

| C3                           | JD(L)           | JFET drain (left)                           |                |     | OD(L) + 2 V            |     |                                 |

| C6                           | JD(R)           | JFET drain (right)                          |                |     | OD(L) + 2 V            |     |                                 |

|                              | onnections      |                                             | I              | 1   |                        |     | 1                               |

| D1, F1                       | Temp            | Temperature sensor                          |                |     | Thermistor             |     |                                 |

| E1                           | -               | No connection                               |                |     | -                      |     |                                 |

If all voltages are set to the typical values operation at, or close to, specification should be obtained. Some adjustment within the minimum - maximum range specified may be required to optimise performance. Refer to the specific device test data if possible. Maximum voltage between pairs of pins: OS to OD  $\pm$  15 V.

Maximum current through any source or drain pin: 10 mA.

The CCD is not electrically connected to the metal package.

#### **NOTES**

- 7. With the RØ connections shown, this device will operate through both outputs simultaneously (split serial mode). To operate from the left-hand output only,  $R\emptyset_1(R)$  and  $R\emptyset_2(R)$  should be reversed, i.e. pin D5 =  $R\emptyset_2(R)$  and E5 =  $R\emptyset_1(R)$ .

- 8. This gate is normally low. It should be pulsed high for charge dump.

- 9. OG2=OG1 + 1 V; for operation in high responsivity, low noise mode. For operation in low responsivity, increased charge handling mode, OG2 should be set high.

- 10. OS = 3 to 5 V below OD typically. Use a 3 5 mA current source or a 5 10 k $\Omega$  load.

- 11. The JFET is floating, with its gate connected to OS. A floating 10 k $\Omega$  load resistor is also connected to OS. The FET may be used to buffer the chip output (OS) if desired; in this case, connect the FET output to A<sub>GND</sub> via a 5 mA load and RL directly to A<sub>GND</sub>. (U309 data:  $V_{GD}$  and  $V_{GS}$  absolute maximum = -25 V). See detail below.

# **DEVICE SCHEMATIC**

# **OUTPUT CIRCUIT**

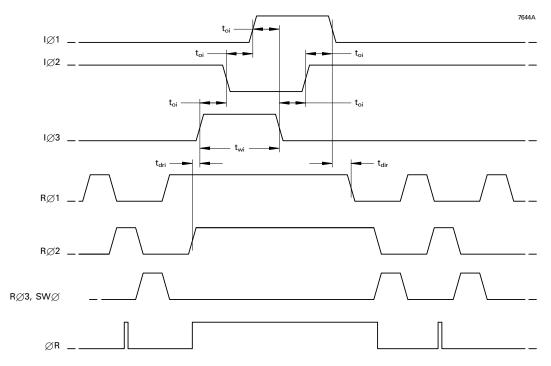

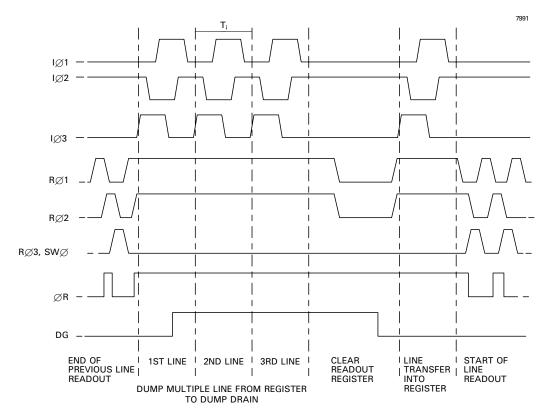

#### FRAME READOUT TIMING DIAGRAM

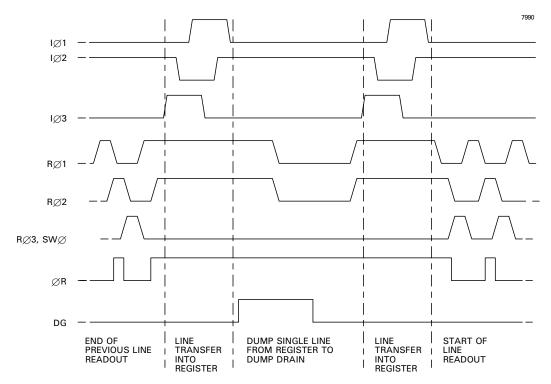

#### **DETAIL OF LINE TRANSFER (Not to scale)**

### NOTES

- 12. Clock edges are defined at mid-amplitude points.

- 13. Rise and fall times should be  $\leqslant$  overlap times.

- 14. Alternate patterns may be used provided sequence and minimum overlaps are maintained.

#### DETAIL OF VERTICAL LINE TRANSFER (Single line dump)

DETAIL OF VERTICAL LINE TRANSFER (Multiple line dump)

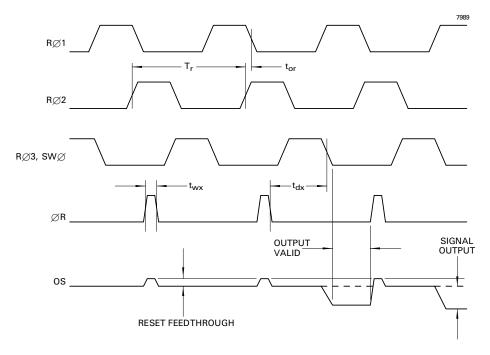

#### **DETAIL OF OUTPUT CLOCKING (Operation through both outputs)**

# LINE OUTPUT FORMAT (Split read-out operation)

# **CLOCK TIMING REQUIREMENTS**

| Symbol                            | Description                             | Min              | Typical            | Max                |    |

|-----------------------------------|-----------------------------------------|------------------|--------------------|--------------------|----|

| T <sub>i</sub>                    | Image clock period                      | 6t <sub>oi</sub> | 100                | see note 15        | μs |

| t <sub>wi</sub>                   | Image clock pulse width                 | 3t <sub>oi</sub> | 50                 | see note 15        | μs |

| t <sub>ri</sub>                   | Image clock pulse rise time (10 to 90%) | 1                | 10                 | 0.5t <sub>oi</sub> | μs |

| t <sub>fi</sub>                   | Image clock pulse fall time (10 to 90%) | t <sub>ri</sub>  | 10                 | 0.5t <sub>oi</sub> | μs |

| t <sub>oi</sub>                   | Image clock pulse overlap               | 5                | 10                 | 0.2T <sub>i</sub>  | μs |

| t <sub>dir</sub>                  | Delay time, IØ stop to RØ start         | 10               | 20                 | see note 15        | μs |

| t <sub>dri</sub>                  | Delay time, RØ stop to IØ start         | 1                | 2                  | see note 15        | μs |

| Tr                                | Output register clock cycle period      | 300              | see note 16        | see note 15        | ns |

| t <sub>rr</sub>                   | Clock pulse rise time (10 to 90%)       | 50               | 0.1T <sub>r</sub>  | 0.3T <sub>r</sub>  | ns |

| t <sub>fr</sub>                   | Clock pulse fall time (10 to 90%)       | t <sub>rr</sub>  | 0.1T <sub>r</sub>  | 0.3T <sub>r</sub>  | ns |

| t <sub>or</sub>                   | Clock pulse overlap                     | 50               | 0.5t <sub>rr</sub> | 0.1T <sub>r</sub>  | ns |

| t <sub>wx</sub>                   | Reset pulse width                       | 50               | 0.1T <sub>r</sub>  | 0.2T <sub>r</sub>  | ns |

| t <sub>rx</sub> , t <sub>fx</sub> | Reset pulse rise and fall times         | 20               | 0.5t <sub>rr</sub> | 0.2T <sub>r</sub>  | ns |

| t <sub>dx</sub>                   | Delay time, ØR low to RØ3 low           | 50               | 0.5T <sub>r</sub>  | 0.8T <sub>r</sub>  | ns |

#### NOTES

- 15. No maximum other than that necessary to achieve an acceptable readout time.

- 16. As set by the readout period (1  $\mu$ s to 100  $\mu$ s is typical).

#### OUTLINE (All dimensions without limits are nominal)

#### (See page 5)

#### **Outline Note**

The device is supplied with shim studs to hold it onto the customer's mounting plate, fitted to three of the four holes as required. The studs are available in two lengths (see dimension AD). The default unless specified is the 15.00 mm stud in the offset position.

#### HANDLING CCD SENSORS

CCD sensors, in common with most high performance MOS IC devices, are static sensitive. In certain cases a discharge of static electricity may destroy or irreversibly degrade the device. The sensor is shipped with a shorting pad on the PGA for electrostatic protection. This must be removed before use. Accordingly, full antistatic handling precautions should be taken whenever using a CCD sensor or module. These include:

- Working at a fully grounded workbench

- Operator wearing a grounded wrist strap

- All receiving socket pins to be positively grounded

- Unattended CCDs should not be left out of their conducting foam or socket.

Evidence of incorrect handling will invalidate the warranty. All devices are provided with internal protection circuits to the gate electrodes (all CCD pins except  $V_{SS}$ , DD, RD, OD and OS) but not to the other pins. See also e2v technologies technical note TN906/419 for information about mosaic assembly.

#### **HIGH ENERGY RADIATION**

Device characteristics will change when subject to ionising radiation.

Users planning to operate CCDs in high radiation environments are advised to contact e2v technologies.

#### **TEMPERATURE LIMITS**

|           |   |  |   |   | Min  | Typical | Max |   |

|-----------|---|--|---|---|------|---------|-----|---|

| Storage   |   |  |   |   | . 73 | -       | 373 | K |

| Operating | • |  | • | • | 153  | 173     | 323 | К |

Operation or storage in humid conditions may give rise to ice on the sensor surface on cooling, causing irreversible damage.

Maximum device heating/cooling . . . 5 K/min

#### MATING CONNECTOR

A custom ZIF connector is available for use with this sensor. The ZIF socket fits within the footprint of the package to optimise close-packing of mosaic assemblies. Contact e2v technologies for details.

Whilst e2v technologies has taken care to ensure the accuracy of the information contained herein it accepts no responsibility for the consequences of any use thereof and also reserves the right to change the specification of goods without notice. e2v technologies accepts no liability beyond that set out in its standard conditions of sale in respect of infringement of third party patents arising from the use of tubes or other devices in accordance with information contained herein.